Dear Customer,

Following the continuous improvement of our Quality and Reliability, we are going to change the Die Attach process and compound from Power Glue to Solder Paste of Power MOSFET Transistors listed in this PCN. Products with new process/material, guarantee the same electrical characteristics as reported in the relevant data sheets. Devices used for qualification are available as Samples.

The involved product series and affected packages are listed in the table below:

| Product Family           | Package           | Commercial Product / Series |

|--------------------------|-------------------|-----------------------------|

| Power MOSFET Transistors | PowerFLAT™ 8x8 HV | STLxxxxxxx                  |

Any other Product related to the above series, manufactured in PowerFLAT<sup>TM</sup> 8x8 HV Package, even if not expressly included or partially mentioned in the attached table, is affected by this change.

# Qualification program and results availability:

The reliability test report is provided in attachment to this document.

### Samples availability:

Samples of the test vehicle devices will be available on request starting from week 28-2018. Any other sample request will be processed and scheduled by Power Transistor Division upon request.

| Product Family Description | Part Number - Test Vehicle |

|----------------------------|----------------------------|

| Dower MOSEET Transisters   | STL57N65M5                 |

| Power MOSFET Transistors   | STL33N60M2                 |

#### **Change implementation schedule:**

The production start and first shipments will be implemented according to our work in progress and materials availability:

| Product Family Description | 1st Shipments     |

|----------------------------|-------------------|

| Power MOSFET Transistors   | From Week 41-2018 |

Lack of acknowledgement of the PCN within 30 days will constitute acceptance of the change. After acknowledgement, lack of additional response within the 90 days period will constitute acceptance of the change (Jedec Standard No. 46-C). In any case, first shipment may start earlier with customer written agreement.

# Marking and traceability:

Unless otherwise stated by customer specific requirement, traceability of PowerFLAT<sup>TM</sup> 8x8 HV Package manufactured with new process/material, will be identified by internal code and the additional info "**P**" marked on the package.

Sincerely Yours.

# RELIABILITY EVALUATION REPORT

New Die Attach process and material evaluation from Power Glue to Solder Paste on PowerFLAT™ 8x8 HV in ASE WEIHAI (China) Subcontractor

**Process Change**

**General Information**

Commercial Product : STL57N65M5 STL33N60M2

**Product Line** : *M5FM01* – *M*Q6701

Product Description : Power MOSFET

Package : PowerFLAT<sup>TM</sup> 8x8 HV

Silicon Technology : MDmesh<sup>TM</sup> M5 MDmesh<sup>TM</sup> M2

**Division** :Power Transistor Division

| Traceability           |                                            |  |

|------------------------|--------------------------------------------|--|

| Diffusion Plant        | : CT8" Catania (Italy)<br>SG6" (Singapore) |  |

| Assembly Plant         | : ASE WEIHAI (China)                       |  |

| Reliability Lab        | : Catania (Italy)                          |  |

| Reliability Assessment |                                            |  |

| Passed                 |                                            |  |

|                        |                                            |  |

**Disclaimer:** this report is a summary of the qualification plan results performed in good faith by STMicroelectronics to evaluate the electronic devices conformance to its specific mission profile for Automotive Application. This report and its contents shall not be disclosed to a third party, except in full, without previous written agreement by STMicroelectronics or under the approval of the author (see below)

#### **REVISION HISTORY**

| Version | Date        | Author       | Changes description |

|---------|-------------|--------------|---------------------|

| 1.0     | 23 May 2018 | A.SETTINIERI | FINAL REPORT        |

#### **APPROVED BY:**

Corrado CAPPELLO ADG Q&R department - Catania STMicroelectronics

# **TABLE OF CONTENTS**

| 1. | RELIA | ABILITY EVALUATION OVERVIEW     | 3 |

|----|-------|---------------------------------|---|

|    | 1.1   | OBJECTIVE                       | 3 |

|    |       | RELIABILITY TEST PLAN           |   |

|    | 1.3   | CONCLUSION                      | 3 |

| 2. | DEVI  | CE/TEST VEHICLE CHARACTERISTICS | 4 |

|    |       | GENERALITIES                    |   |

|    | 2.2   | PIN CONNECTION                  | 4 |

|    |       | TRACEABILITY                    |   |

| 3. | TEST  | S RESULTS SUMMARY               | 6 |

|    | 3.1   | LOT INFORMATION                 | 6 |

|    | 3.2   | TEST RESULTS SUMMARY            | 6 |

# 1. RELIABILITY EVALUATION OVERVIEW

# 1.1 Objective

Reliability evaluation to verify the new die attach process and material from Power Glue to Solder Paste on PowerFLAT<sup>TM</sup> 8x8 HV assembled in ASE WEIHAI (China) Subcontractor.

# 1.2 Reliability Test Plan

Reliability tests performed on this device are in agreement with JESD47 and internal spec 0061692 and are listed in the Test Plan.

For details on test conditions, generic data used and spec reference see test results summary at Par.3.

| # | Stress                                 | Abrv | Reference                                               | Test Flag | Comments |

|---|----------------------------------------|------|---------------------------------------------------------|-----------|----------|

| 1 | Pre and Post-Stress Electrical<br>Test | TEST | User specification or supplier's standard Specification |           |          |

| 2 | External Visual                        | EV   | JESD22B-101                                             | 1         |          |

| 3 | Pre-conditioning                       | PC   | JESD22A-113                                             | 1         |          |

| 4 | Temperature Cycling                    | TC   | JESD22A-104                                             | 1         |          |

| 5 | Autoclave                              | AC   | JESD22A-102                                             | 1         |          |

| 6 | Intermittent Operating Life Test       | IOL  | MIL-STD-750 Method<br>1037                              | 1         |          |

#### 1.3 Conclusion

All reliability tests have been completed with positive results. Neither functional nor parametric rejects were detected at final electrical testing.

Parameter drift analysis performed on samples submitted to package oriented test showed a good stability of the main electrical monitored parameters.

Package oriented tests have not put in evidence any criticality.

On the basis of the overall results obtained, we can give a positive judgment on the reliability evaluation for New Die Attach process with Solder Paste on medium/large die size assembled in Power FLAT<sup>TM</sup> 8x8 HV of ASE WEIHAI (China) Subcontractor, in agreement with JESD47 and internal spec 0061692

Choose an item. RER Id. N.:202B/2018

# 2. DEVICE/TEST VEHICLE CHARACTERISTICS

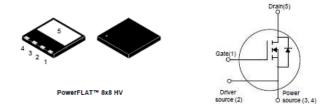

#### 2.1 Generalities

Power MOSFET MDmesh<sup>TM</sup> M5 / MDmesh<sup>TM</sup> M2

# 2.2 Pin Connection

# 2.3 Traceability

Reference "Product Baseline" document if existing, else provide following chapters/information:

#### D.U.T.: STL57N65M5

PACKAGE: PowerFLAT™ 8x8 HV

#### Wafer fab information

| Wafer fab information                  |                             |

|----------------------------------------|-----------------------------|

| Wafer fab manufacturing location       | CT8" Catania (Italy)        |

| Wafer diameter (inches)                | 8"                          |

| Silicon process technology             | Power MOSFET MDmesh™ M5     |

| Die finishing front side (passivation) | Nitride                     |

| Die finishing back side                | Ti/Ni/Ag                    |

| Die area (Stepping die size)           | 7340 x 4750 μm <sup>2</sup> |

| Metal levels/Materials                 | AlCu/Ti/TiN                 |

### Assembly information

| Assembly information              |                     |  |

|-----------------------------------|---------------------|--|

| Assembly Information              |                     |  |

| Assembly plant location           | ASE WEIHAI (China)  |  |

| Package code description          | PowerFLAT™ 8x8 HV   |  |

| Leadframe/Substrate               | Copper              |  |

| Die attach material               | Solder Paste        |  |

| Wires bonding materials/diameters | Cu / 2 mils         |  |

| Molding compound                  | HF Molding compound |  |

D.U.T.: STL33N60M2 PACKAGE: PowerFLAT<sup>TM</sup> 8x8 HV

### Wafer fab information

| valor lab information                  |                             |  |

|----------------------------------------|-----------------------------|--|

| Wafer fab information                  |                             |  |

| Wafer fab manufacturing location       | SG6" (Singapore)            |  |

| Wafer diameter (inches)                | 6"                          |  |

| Silicon process technology             | Power MOSFET MDmesh™ M2     |  |

| Die finishing front side (passivation) | Nitride                     |  |

| Die finishing back side                | Ti/Ni/Ag                    |  |

| Die area (Stepping die size)           | 5630 x 4580 μm <sup>2</sup> |  |

| Metal levels/Materials                 | AlSi                        |  |

#### Assembly information

| Assembly Information              |                     |

|-----------------------------------|---------------------|

| Assembly plant location           | ASE WEIHAI (China)  |

| Package code description          | PowerFLAT™ 8x8 HV   |

| Leadframe/Substrate               | Copper              |

| Die attach material               | Solder Paste        |

| Wires bonding materials/diameters | Cu / 2 mils         |

| Molding compound                  | HF Molding compound |

#### Reliability testing information

| Reliability Testing Information |                 |

|---------------------------------|-----------------|

| Reliability laboratory location | Catania (Italy) |

| Electrical testing location     | Catania (Italy) |

# 3. TESTS RESULTS SUMMARY

# 3.1 Lot Information

| Lot # | Product line | Package           | Wafer Fab           | Assembly plant        | Note |

|-------|--------------|-------------------|---------------------|-----------------------|------|

| 1     | NACENAGA     | PowerFLAT™ 8x8 HV | CT8" - M5           |                       |      |

| 2     | M5FM01       |                   | Catania (Italy)     | ASE WEIHAI<br>(China) |      |

| 3     | MQ6701       |                   | SG6"<br>(Singapore) | (Chillia)             |      |

# 3.2 Test results summary

Test plan results are summarized in the following template.

|                        | РС | Std ref.                   | Conditions                                                                                   | SS                                                  | Steps  | Failure/SS |       |       |  |

|------------------------|----|----------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------|--------|------------|-------|-------|--|

| Test                   |    |                            |                                                                                              |                                                     |        | Lot 1      | Lot 2 | Lot 3 |  |

| TEST                   |    | User specification         | All qualification parts tested per the requirements of the appropriate device specification. |                                                     |        | 75         | 75    | 75    |  |

| External visual        |    | JESD22<br>B-101            | All devices submitted for testing                                                            |                                                     |        | 75         | 75    | 75    |  |

| Package Oriented Tests |    |                            |                                                                                              |                                                     |        |            |       |       |  |

| PC                     |    | JESD22<br>A-113            | 40 H @ Ta=60°C Rh=60%<br>Over Reflow @ Tpeak=260°C<br>3 times                                | All devices to<br>be subjected<br>to TC, IOL,<br>AC | FINAL  | Pass       | Pass  | Pass  |  |

| TC                     | Υ  | JESD22<br>A-104            | TA = -65°C to 150°C                                                                          | 75                                                  | 500 cy | 0/25       | 0/25  | 0/25  |  |

| IOL                    | Υ  | MIL-STD-750<br>Method 1037 | ΔTC=105°C                                                                                    | 75                                                  | 10kcy  | 0/25       | 0/25  | 0/25  |  |

| AC                     | Υ  | JESD22<br>A-102            | Pa=2Atm / TA=121°C                                                                           | 75                                                  | 96 H   | 0/25       | 0/25  | 0/25  |  |